Question 16133 – Cache

November 12, 2023Question 16161 – RISC-and-CISC

November 12, 2023Question 10934 – Cache

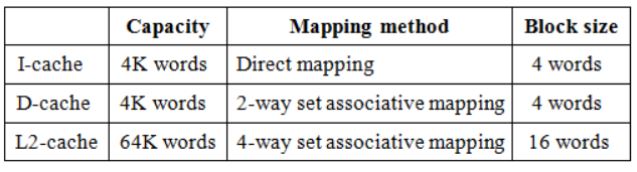

A computer system has a level-1 instruction cache (1-cache), a level-1 data cache (D-cache) and a level-2 cache (L2-cache) with the following specifications:

The length of the physical address of a word in the main memory is 30 bits. The capacity of the tag memory in the I-cache, D-cache and L2-cache is, respectively,

Correct Answer: A

Question 24 Explanation:

No. of blocks in cache = Capacity/Block size = 2m

Bits to represent blocks = m

No. of words in a block = 2n

Bits to represent a word = n

Tag bits = (length of physical address of a word) – (bits to represent blocks) – (bits to represent a word)

⇒ Each block will have its own tag bits.

So, total tag bits = no. of blocks × tag bits.

Bits to represent blocks = m

No. of words in a block = 2n

Bits to represent a word = n

Tag bits = (length of physical address of a word) – (bits to represent blocks) – (bits to represent a word)

⇒ Each block will have its own tag bits.

So, total tag bits = no. of blocks × tag bits.

1K × 18-bit, 1K × 19-bit, 4K × 16-bit

1K × 16-bit, 1K × 19-bit, 4K × 18-bit

1K × 16-bit, 512 × 18-bit, 1K × 16-bit

1K × 18-bit, 512 × 18-bit, 1K × 18-bit