UGC NET CS 2005 Dec-Paper-2

March 31, 2024Question 4596 – UGC NET CS 2006 June-Paper-2

March 31, 2024UGC NET CS 2005 Dec-Paper-2

|

Question 7

|

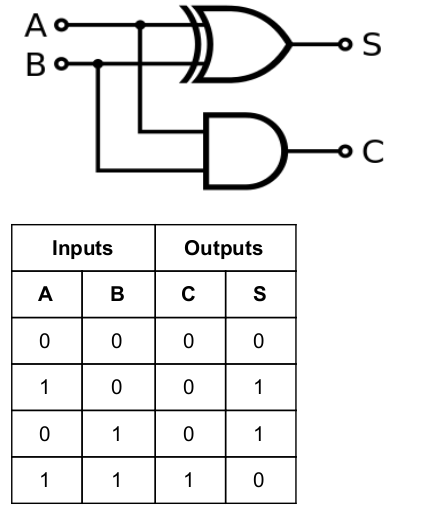

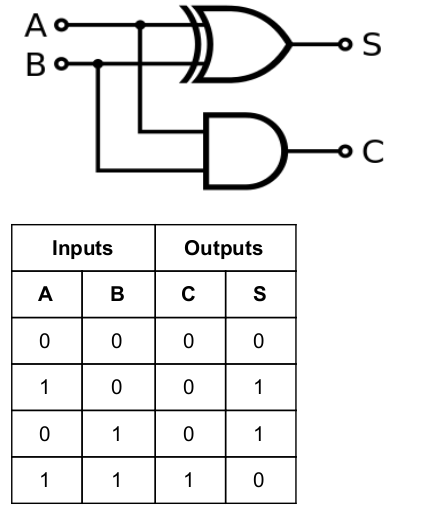

A half-adder is also known as :

|

AND Circuit

|

|

|

NAND Circuit

|

|

|

NOR Circuit

|

|

|

EX-OR Circuit

|

Question 7 Explanation:

→ The half adder adds two single binary digits A and B. It has two outputs, sum (S) and carry (C). The carry signal represents an overflow into the next digit of a multi-digit addition. The value

of the sum is 2C + S. The simplest half-adder design incorporates an XOR gate for S and an AND gate for C. The Boolean logic for the sum (in this case S) will be A′B + AB′ whereas for the carry (C) will be AB.

of the sum is 2C + S. The simplest half-adder design incorporates an XOR gate for S and an AND gate for C. The Boolean logic for the sum (in this case S) will be A′B + AB′ whereas for the carry (C) will be AB.

Correct Answer: D

Question 7 Explanation:

→ The half adder adds two single binary digits A and B. It has two outputs, sum (S) and carry (C). The carry signal represents an overflow into the next digit of a multi-digit addition. The value

of the sum is 2C + S. The simplest half-adder design incorporates an XOR gate for S and an AND gate for C. The Boolean logic for the sum (in this case S) will be A′B + AB′ whereas for the carry (C) will be AB.

of the sum is 2C + S. The simplest half-adder design incorporates an XOR gate for S and an AND gate for C. The Boolean logic for the sum (in this case S) will be A′B + AB′ whereas for the carry (C) will be AB.