GATE 2011

March 13, 2025GATE 2011

March 13, 2025GATE 2011

|

Question 30

|

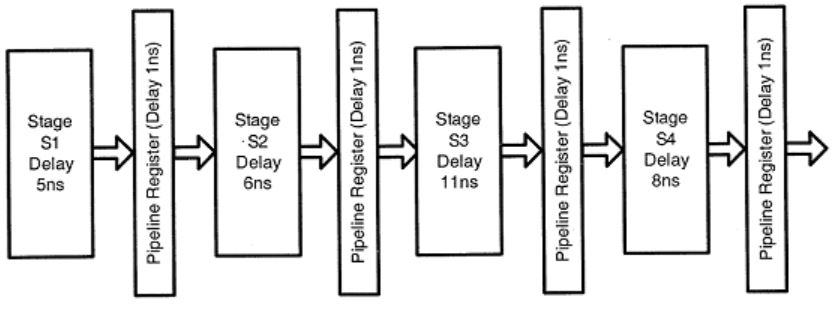

Consider an instruction pipeline with four stages (S1, S2, S3 and S4) each with combinational circuit only. The pipeline registers are required between each stage and at the end of the last stage. Delays for the stages and for the pipeline registers are as given in the figure:

What is the approximate speed up of the pipeline in steady state under ideal conditions when compared to the corresponding non-pipeline implementation?

|

4.0

|

|

|

2.5

|

|

|

1.1

|

|

|

3.0

|

Question 30 Explanation:

Speedup = Time without pipelining/Time with pipelining

Clock cycle time of pipelining

= max (5ns, 6ns, 11ns, 8ns) + 1ns

= 11 + 1

= 12ns

Time without pipelining = 5 + 6 + 11 + 8 = 30 ns

∴ Speedup = 30/12 = 2.5

Clock cycle time of pipelining

= max (5ns, 6ns, 11ns, 8ns) + 1ns

= 11 + 1

= 12ns

Time without pipelining = 5 + 6 + 11 + 8 = 30 ns

∴ Speedup = 30/12 = 2.5

Correct Answer: B

Question 30 Explanation:

Speedup = Time without pipelining/Time with pipelining

Clock cycle time of pipelining

= max (5ns, 6ns, 11ns, 8ns) + 1ns

= 11 + 1

= 12ns

Time without pipelining = 5 + 6 + 11 + 8 = 30 ns

∴ Speedup = 30/12 = 2.5

Clock cycle time of pipelining

= max (5ns, 6ns, 11ns, 8ns) + 1ns

= 11 + 1

= 12ns

Time without pipelining = 5 + 6 + 11 + 8 = 30 ns

∴ Speedup = 30/12 = 2.5