GATE 2022

October 4, 2023UGC-NET DEC-2019 Part-2

October 4, 2023Operating-Systems

|

Question 422

|

Computer uses 46-bit virtual address, 32 bit physical address, and a three level paged page table organization. The page table base register stores the base address of the first level table(T1), which occupies exactly one page. Each entry of T1 stores the base address of a page of the second level table (T2). Each entry of T2 stores the base address of a page of the third level table(T3). Each entry of T3 stores a page table entry(PTE). The PTE is 32 bits in size, The processor used in the computer has a 1MB 16 way set associative virtually indexed physically tagged cache. the cache block size is 64 bytes.

What is the size of a page in KB in this computer?

|

2

|

|

|

4

|

|

|

8

|

|

|

16

|

Question 422 Explanation:

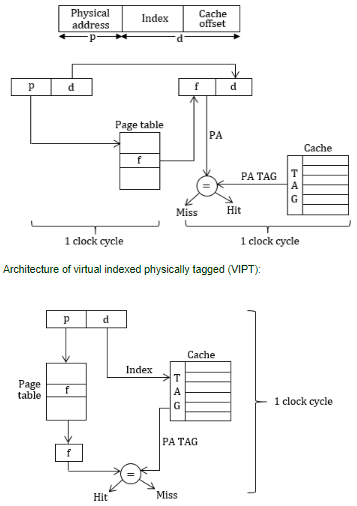

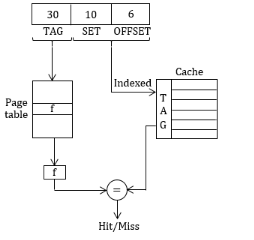

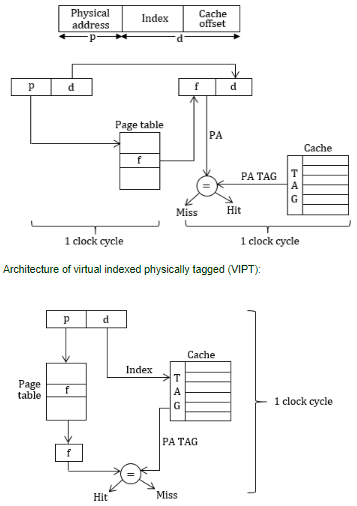

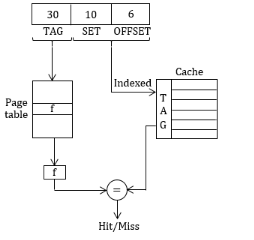

Architecture of physically indexed cache:

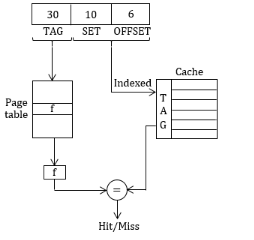

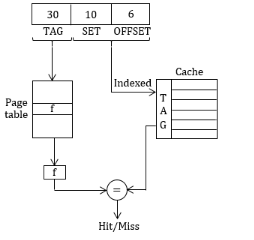

VIPT cache and aliasing effect and synonym.

Alias: Same physical address can be mapped to multiple virtual addresses.

Synonym: Different virtual addresses mapped to same physical address (for data sharing).

So these synonyms should be in same set to avoid write-update problems.

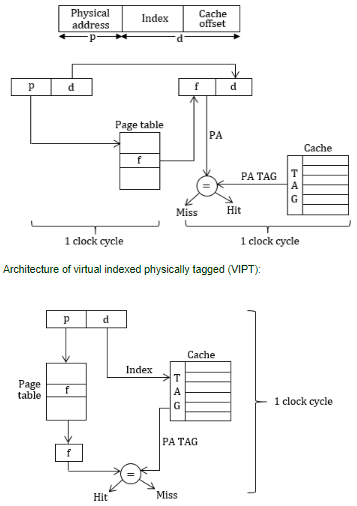

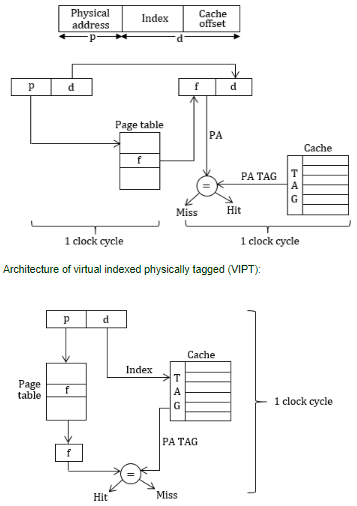

In our problem VA = 46bits

We are using 16 bits for indexing into cache.

To have two synonym is same set we need to have same 16 bits index for PA & VA.

Assume that physical pages are colored and each set should have pages of same color so that any synonyms are in same set.

Since page size = 8KB ⇒ 13 bits

These 13bits are not translated during VA→PA. So 13 bits are same out of 16 Index bits, 13 are same we need to make 3 bits (16-13) same now.

3 bits can produce, 23 = 8 combinations which can be mapped on the different sets, so we need 8 different colors to color our pages. >br> In physically indexed cache indexing is done via physical address bits, but in virtual indexed cache, cache is indexed from (offset + set) bits. In physical Index cache indexing is done one to one (1 index maps to one page in one block of cache). In VIPT we have more/ extra bits, so mapping is not one-one. Hence these extra bits have to be taken care, such that if two virtual address refers to same page in cache block of different sets then they have to be assumed same i.e., we say of same color and put same color page in one set to avoid write update problems.

VIPT cache and aliasing effect and synonym.

Alias: Same physical address can be mapped to multiple virtual addresses.

Synonym: Different virtual addresses mapped to same physical address (for data sharing).

So these synonyms should be in same set to avoid write-update problems.

In our problem VA = 46bits

We are using 16 bits for indexing into cache.

To have two synonym is same set we need to have same 16 bits index for PA & VA.

Assume that physical pages are colored and each set should have pages of same color so that any synonyms are in same set.

Since page size = 8KB ⇒ 13 bits

These 13bits are not translated during VA→PA. So 13 bits are same out of 16 Index bits, 13 are same we need to make 3 bits (16-13) same now.

3 bits can produce, 23 = 8 combinations which can be mapped on the different sets, so we need 8 different colors to color our pages. >br> In physically indexed cache indexing is done via physical address bits, but in virtual indexed cache, cache is indexed from (offset + set) bits. In physical Index cache indexing is done one to one (1 index maps to one page in one block of cache). In VIPT we have more/ extra bits, so mapping is not one-one. Hence these extra bits have to be taken care, such that if two virtual address refers to same page in cache block of different sets then they have to be assumed same i.e., we say of same color and put same color page in one set to avoid write update problems.

Correct Answer: C

Question 422 Explanation:

Architecture of physically indexed cache:

VIPT cache and aliasing effect and synonym.

Alias: Same physical address can be mapped to multiple virtual addresses.

Synonym: Different virtual addresses mapped to same physical address (for data sharing).

So these synonyms should be in same set to avoid write-update problems.

In our problem VA = 46bits

We are using 16 bits for indexing into cache.

To have two synonym is same set we need to have same 16 bits index for PA & VA.

Assume that physical pages are colored and each set should have pages of same color so that any synonyms are in same set.

Since page size = 8KB ⇒ 13 bits

These 13bits are not translated during VA→PA. So 13 bits are same out of 16 Index bits, 13 are same we need to make 3 bits (16-13) same now.

3 bits can produce, 23 = 8 combinations which can be mapped on the different sets, so we need 8 different colors to color our pages. >br> In physically indexed cache indexing is done via physical address bits, but in virtual indexed cache, cache is indexed from (offset + set) bits. In physical Index cache indexing is done one to one (1 index maps to one page in one block of cache). In VIPT we have more/ extra bits, so mapping is not one-one. Hence these extra bits have to be taken care, such that if two virtual address refers to same page in cache block of different sets then they have to be assumed same i.e., we say of same color and put same color page in one set to avoid write update problems.

VIPT cache and aliasing effect and synonym.

Alias: Same physical address can be mapped to multiple virtual addresses.

Synonym: Different virtual addresses mapped to same physical address (for data sharing).

So these synonyms should be in same set to avoid write-update problems.

In our problem VA = 46bits

We are using 16 bits for indexing into cache.

To have two synonym is same set we need to have same 16 bits index for PA & VA.

Assume that physical pages are colored and each set should have pages of same color so that any synonyms are in same set.

Since page size = 8KB ⇒ 13 bits

These 13bits are not translated during VA→PA. So 13 bits are same out of 16 Index bits, 13 are same we need to make 3 bits (16-13) same now.

3 bits can produce, 23 = 8 combinations which can be mapped on the different sets, so we need 8 different colors to color our pages. >br> In physically indexed cache indexing is done via physical address bits, but in virtual indexed cache, cache is indexed from (offset + set) bits. In physical Index cache indexing is done one to one (1 index maps to one page in one block of cache). In VIPT we have more/ extra bits, so mapping is not one-one. Hence these extra bits have to be taken care, such that if two virtual address refers to same page in cache block of different sets then they have to be assumed same i.e., we say of same color and put same color page in one set to avoid write update problems.