Virtual Memory

Question 1 |

In a virtual memory system the address space specified by the address lines of the CUP must be __________ than the physical memory size and _______ than the secondary storage size.

smaller, smaller | |

smaller, larger | |

larger, smaller | |

larger, larger |

Question 2 |

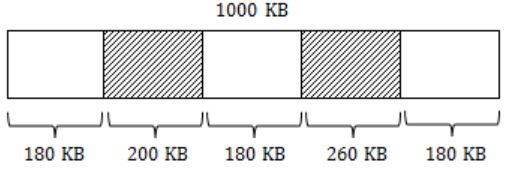

A 1000 Kbyte memory is managed using variable partitions but to compaction. It currently has two partitions of sizes 200 Kbytes and 260 Kbytes respectively. The smallest allocation request in Kbytes that could be denied is for

151 | |

181 | |

231 | |

541 |

So, smallest allocation request which can be denied is 181 KB.

Question 3 |

Dirty bit for a page in a page table

helps avoid unnecessary writes on a paging device | |

helps maintain LRU information | |

allows only read on a page | |

None of the above |

Question 4 |

Consider a process executing on an operating system that uses demand paging. The average time for a memory access in the system is M units if the corresponding memory page is available in memory and D units if the memory access causes a page fault. It has been experimentally measured that the average time taken for a memory access in the process is X units.

Which one of the following is the correct expression for the page fault rate experienced by the process?

(D-M)/(X-M) | |

(X-M)/(D-M) | |

(D-X)/(D-M) | |

(X-M)/(D-X) |

X = (1 - P)M + D × P

X = M ∙ PM + DP

(X - M) = P(D - M)

⇒ P = (X - M) / (D - M)

Question 5 |

If an instruction takes i microseconds and a page fault takes an additional j microseconds, the effective instruction time if on the average a page fault occurs every k instruction is:

i + (j/k) | |

i + (j*k) | |

(i+j)/ k | |

(i+j)*k |

= service time + page fault rate * page fault service time

= i + 1/k * j

= i + j/k

or

The effective instruction time, if on the average a page fault occurs every k instructions, is:

i + (j / k)

This formula accounts for the normal instruction time (i) and the additional time for a page fault (j), considering the average frequency of page faults (k instructions between page faults).

Question 6 |

A multi-user, multi-processing operating system cannot be implemented on hardware that does not support

Address translation | |

DMA for disk transfer | |

At least two modes of CPU execution (privileged and non-privileged) | |

Demand paging | |

Both A and C |

Question 7 |

Which of the following is/are advantage of virtual memory?

Faster access to memory on an average. | |

Processes can be given protected address spaces. | |

Linker can assign addresses independent of where the program will be loaded in physical memory. | |

Programs larger than the physical memory size can be run. | |

Both B and D |

B) True. Because in virtual memory concept of address translation provides protected address space so that one process do not interfere the other process.

C) False.

D) True.

Question 8 |

A certain computer system has the segmented paging architecture for virtual memory. The memory is byte addressable. Both virtual and physical address spaces contain 216 bytes each. The virtual address space is divided into 8 non-overlapping equal size segments. The memory management unit (MMU) has a hardware segment table, each entry of which contains the physical address of the page table for the segments. Page tables are stored in the main memory and consists of 2 byte page table entries.

(a) What is the minimum page size in bytes so that the page table for a segment requires at most one page to store it? Assume that the page size can only be a power of 2.

(b) Now suppose that the pages size is 512 bytes. It is proposed to provide a TLB (Transaction look-aside buffer) for speeding up address translation. The proposed TLB will be capable of storing page table entries for 16 recently referenced virtual pages, in a fast cache that will use the direct mapping scheme. What is the number of tag bits that will need to be associated with each cache entry?

(c) Assume that each page table entry contains (besides other information) 1 valid bit, 3 bits for page protection and 1 dirty bit. How many bits are available in page table entry for storing the aging information for the page? Assume that the page size is 512 bytes.

Theory Explanation. |

Question 9 |

Suppose the time to service a page fault is on the average 10 milliseconds, while a memory access takes 1 microsecond. Then a 99.99% hit ratio results in average memory access time of

1.9999 milliseconds | |

1 millisecond | |

9.999 microseconds | |

1.9999 microseconds |

= (0.9999*1) + [(1-0.9999) *10000]

= (0.9999) + (0.0001 * 10000)

= 0.9999 + 1

= 1.9999 microseconds

Question 10 |

Which of the following statements is false?

Virtual memory implements the translation of a program’s address space into physical memory address space | |

Virtual memory allows each program to exceed the size of the primary memory | |

Virtual memory increases the degree of multiprogramming | |

Virtual memory reduces the context switching overhead |

Question 11 |

In a system with 32 bit virtual addresses and 1 KB page size, use of one-level page tables for virtual to physical address translation is not practical because of

the large amount of internal fragmentation | |

the large amount of external fragmentation | |

the large memory overhead in maintaining page tables | |

the large computation overhead in the translation process

|

Virtual address = 32 bit = 232

No. of page level entries = 232 / 210

= 222

= 4M (Too large size)

Question 12 |

A processor uses 2-level page tables for virtual to physical address translation. Page tables for both levels are stored in the main memory. Virtual and physical addresses are both 32 bits wide. The memory is byte addressable. For virtual to physical address translation, the 10 most significant bits of the virtual address are used as index into the first level page table while the next 10 bits are used as index into the second level page table. The 12 least significant bits of the virtual address are used as offset within the page. Assume that the page table entries in both levels of page tables are 4 bytes wide. Further, the processor has a translation look-aside buffer (TLB), with a hit rate of 96%. The TLB caches recently used virtual page numbers and the corresponding physical page numbers. The processor also has a physically addressed cache with a hit rate of 90%. Main memory access time is 10 ns, cache access time is 1 ns, and TLB access time is also 1 ns.

Assuming that no page faults occur, the average time taken to access a virtual address is approximately (to the nearest 0.5 ns)

1.5 ns | |

2 ns | |

3 ns | |

4 ns |

(TLB Miss * Cache Hit) + (TLB Miss * Cache Miss)

= (0.96*0.9*2)+(0.96*0.1+12)

(0.04*0.9*2)+(0.04*0.1*32)

= 3.8

= 4 (approximately)