GATE 2009

October 15, 2023NIC-NIELIT Scientist-B 2020

October 15, 2023Digital-Logic-Design

|

Question 120

|

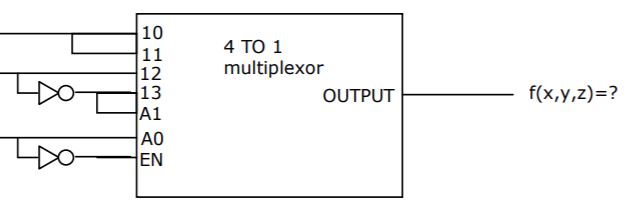

Consider the following multiplexor where 10, 11, 12, 13 are four data input lines selected by two address line combinations A1A0 = 00,01,10,11 respectively and f is “the output of the multiplexor. EN is the enable input.

The function f(x,y,z) implemented by the above circuit is:

|

xyz’

|

|

|

xy+z

|

|

|

x+y

|

|

|

None of the above

|

Question 120 Explanation:

F = (A’A0’10 + A’A0’11 + A’A0’12 + A1A013) EN

F = (xyz’ + xyz + y’zy + zy’)z’

= (xyz’ + xyz + y’z(y+1))z’

= (xyz’ + xyz + y’z)z’

= (xy(z+z’) + y’z)z’

= (xy + y’z)z’

= (xyz’ + y’zz’)

= (xyz’)

F = (xyz’ + xyz + y’zy + zy’)z’

= (xyz’ + xyz + y’z(y+1))z’

= (xyz’ + xyz + y’z)z’

= (xy(z+z’) + y’z)z’

= (xy + y’z)z’

= (xyz’ + y’zz’)

= (xyz’)

Correct Answer: A

Question 120 Explanation:

F = (A’A0’10 + A’A0’11 + A’A0’12 + A1A013) EN

F = (xyz’ + xyz + y’zy + zy’)z’

= (xyz’ + xyz + y’z(y+1))z’

= (xyz’ + xyz + y’z)z’

= (xy(z+z’) + y’z)z’

= (xy + y’z)z’

= (xyz’ + y’zz’)

= (xyz’)

F = (xyz’ + xyz + y’zy + zy’)z’

= (xyz’ + xyz + y’z(y+1))z’

= (xyz’ + xyz + y’z)z’

= (xy(z+z’) + y’z)z’

= (xy + y’z)z’

= (xyz’ + y’zz’)

= (xyz’)