Pipelining

October 19, 2023Pipelining

October 19, 2023Pipelining

|

Question 16

|

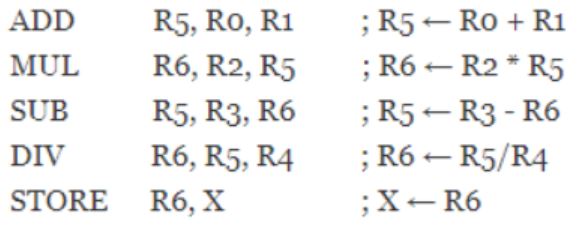

A pipelined processor uses a 4-stage instruction pipeline with the following stages: Instruction fetch (IF), Instruction decode (ID), Execute (EX) and Writeback (WB). The arithmetic operations as well as the load and store operations are carried out in the EX stage. The sequence of instructions corresponding to the statement X = (S – R * (P + Q))/T is given below. The values of variables P, Q, R, S and T are available in the registers R0, R1, R2, R3 and R4 respectively, before the execution of the instruction sequence.

The number of Read-After-Write (RAW) dependencies, Write-After-Read( WAR) dependencies, and Write-After-Write (WAW) dependencies in the sequence of instructions are, respectively,

|

2, 2, 4

|

|

|

3, 2, 3

|

|

|

4, 2, 2

|

|

|

3, 3, 2

|

Question 16 Explanation:

RAW:

I1 – I2 (R5)

I2 – I3 (R6)

I3 – I4 (R5)

I4 – I5 (R6)

WAR:

I2 – I3 (R5)

I3 – I4 (R6)

WAW:

I1 – I3 (R5)

I3 – I4 (R6)

I1 – I2 (R5)

I2 – I3 (R6)

I3 – I4 (R5)

I4 – I5 (R6)

WAR:

I2 – I3 (R5)

I3 – I4 (R6)

WAW:

I1 – I3 (R5)

I3 – I4 (R6)

Correct Answer: C

Question 16 Explanation:

RAW:

I1 – I2 (R5)

I2 – I3 (R6)

I3 – I4 (R5)

I4 – I5 (R6)

WAR:

I2 – I3 (R5)

I3 – I4 (R6)

WAW:

I1 – I3 (R5)

I3 – I4 (R6)

I1 – I2 (R5)

I2 – I3 (R6)

I3 – I4 (R5)

I4 – I5 (R6)

WAR:

I2 – I3 (R5)

I3 – I4 (R6)

WAW:

I1 – I3 (R5)

I3 – I4 (R6)