Operating-Systems

October 19, 2023Pipelining

October 19, 2023Pipelining

|

Question 15

|

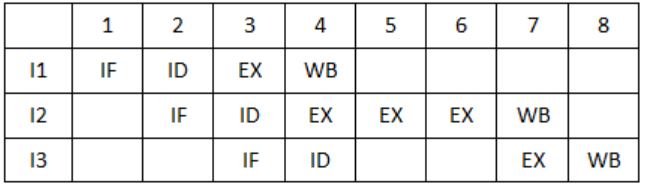

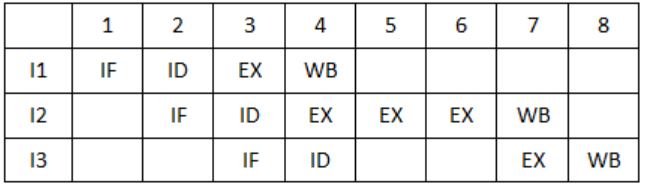

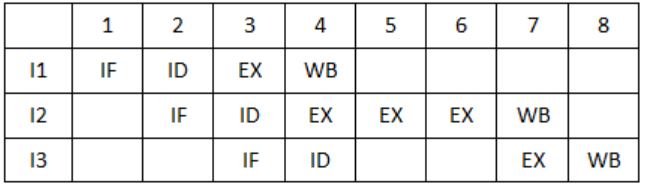

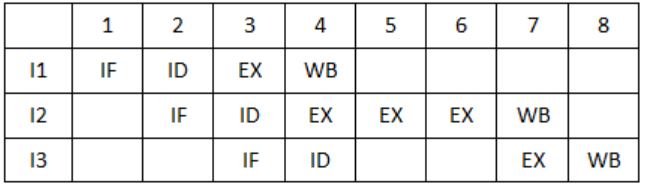

Consider a pipelined processor with the following four stages:

IF: Instruction Fetch ID: Instruction Decode and Operand Fetch EX: Execute WB: Write Back

The IF, ID and WB stages take one clock cycle each to complete the operation. The number of clock cycles for the EX stage depends on the instruction. The ADD and SUB instructions need 1 clock cycle and the MUL instruction needs 3 clock cycles in the EX stage. Operand forwarding is used in the pipelined processor. What is the number of clock cycles taken to complete the following sequence of instructions?

ADD R2, R1, R0 R2 <- R0 + R1 MUL R4, R3, R2 R4 <- R3 * R2 SUB R6, R5, R4 R6 <- R5 - R4

|

7

|

|

|

8

|

|

|

10

|

|

|

14

|

Question 15 Explanation:

Since operand forwarding is there, by default we consider the operand forwarding from EX stage to EX stage.

So, total no. of clock cycles needed to execute the given 3 instructions is 8.

So, total no. of clock cycles needed to execute the given 3 instructions is 8.

Correct Answer: B

Question 15 Explanation:

Since operand forwarding is there, by default we consider the operand forwarding from EX stage to EX stage.

So, total no. of clock cycles needed to execute the given 3 instructions is 8.

So, total no. of clock cycles needed to execute the given 3 instructions is 8.