Software-Engineering

March 15, 2024UGC NET CS 2016 July- paper-2

March 15, 2024UGC NET CS 2016 July- paper-2

|

Question 10

|

In a positive-edge-triggered JK flip-flop, if J and K both are high then the output will be _____ on the rising edge of the clock.

|

No change

|

|

|

Set

|

|

|

Reset

|

|

|

Toggle

|

Question 10 Explanation:

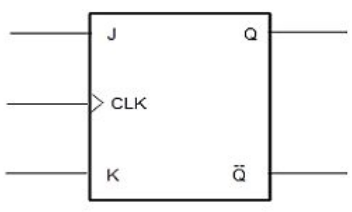

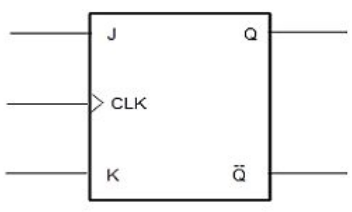

Positive-edge-triggered JK flip-flop is

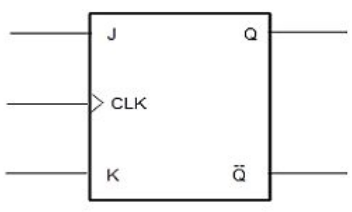

The Truth Table for the JK Function

When J = 1 and K = 1 , The output continuously Toggles from 1 to 0 and 0 to 1. At the end Output is indeterminate. This condition is called as Race around Condition. This happens when Propagation

Delay is less than the Pulse width.

The Truth Table for the JK Function

When J = 1 and K = 1 , The output continuously Toggles from 1 to 0 and 0 to 1. At the end Output is indeterminate. This condition is called as Race around Condition. This happens when Propagation

Delay is less than the Pulse width.

Correct Answer: D

Question 10 Explanation:

Positive-edge-triggered JK flip-flop is

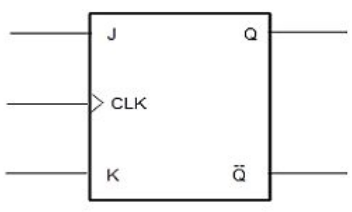

The Truth Table for the JK Function

When J = 1 and K = 1 , The output continuously Toggles from 1 to 0 and 0 to 1. At the end Output is indeterminate. This condition is called as Race around Condition. This happens when Propagation

Delay is less than the Pulse width.

The Truth Table for the JK Function

When J = 1 and K = 1 , The output continuously Toggles from 1 to 0 and 0 to 1. At the end Output is indeterminate. This condition is called as Race around Condition. This happens when Propagation

Delay is less than the Pulse width.