Theory-of-Computation

October 12, 2023UML

October 12, 2023GATE 2023

|

Question 42

|

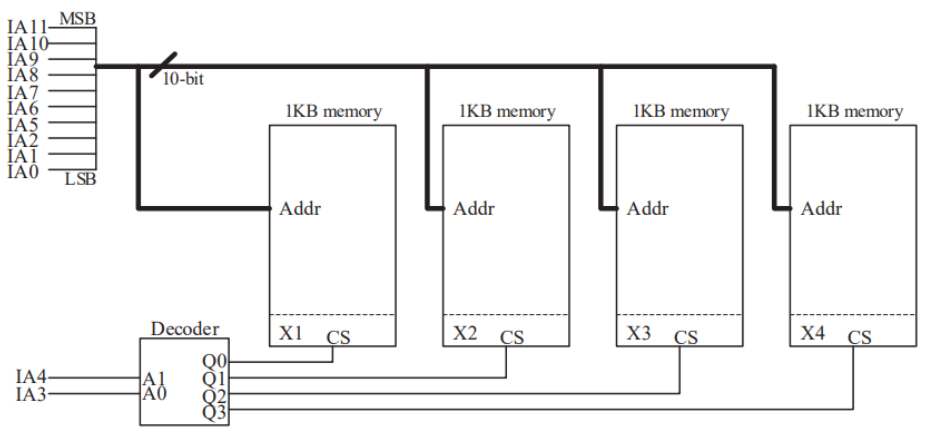

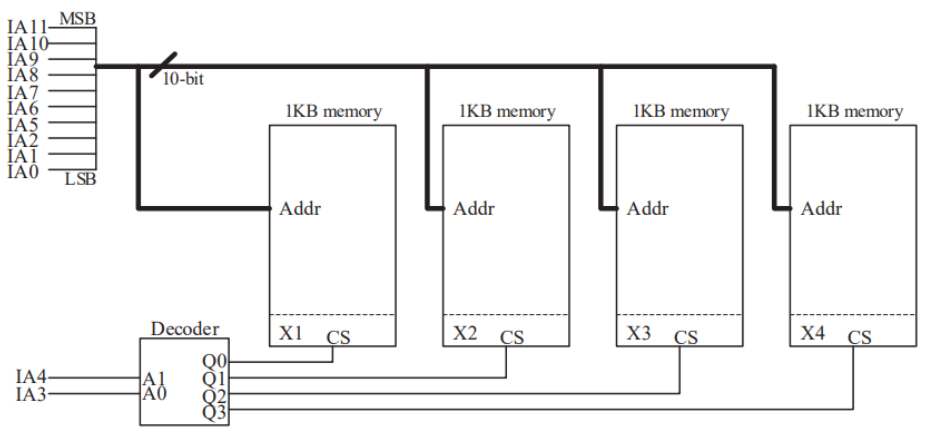

A 4 kilobyte (KB) byte-addressable memory is realized using four 1 KB memory blocks. Two input address lines (IA4 and IA3) are connected to the chip select (CS) port of these memory blocks through a decoder as shown in the figure. The remaining ten input address lines from IA11–IA0 are connected to the address port of these blocks. The chip select (CS) is active high.

The input memory addresses (IA11–IA0), in decimal, for the starting locations (Addr=0) of each block (indicated as X1, X2, X3, X4 in the figure) are among the options given below. Which one of the following options is CORRECT?

The input memory addresses (IA11–IA0), in decimal, for the starting locations (Addr=0) of each block (indicated as X1, X2, X3, X4 in the figure) are among the options given below. Which one of the following options is CORRECT?

|

(0, 1, 2, 3)

|

|

|

(0, 1024, 2048, 3072)

|

|

|

(0, 8, 16, 24)

|

|

|

(0, 0, 0, 0)

|

Correct Answer: C