E-commerce

December 17, 2023Question 9626 – Machine-Instructions

December 18, 2023Machine-Instructions

|

Question 2

|

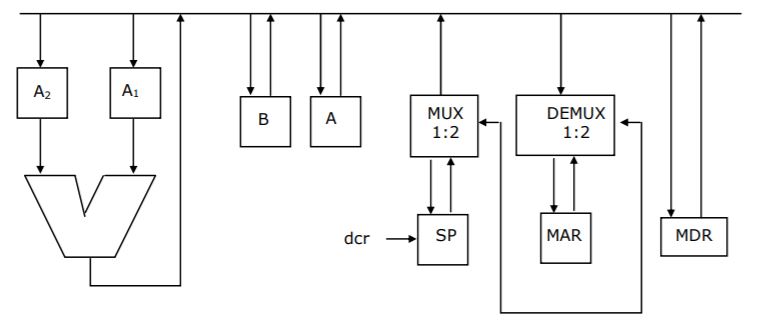

Consider the following data path of a simple non-pilelined CPU. The registers A, B, A1, A2, MDR, the bus and the ALU are 8-bit wide. SP and MAR are 16-bit registers. The MUX is of size 8 × (2:1) and the DEMUX is of size 8 × (1:2). Each memory operation takes 2 CPU clock cycles and uses MAR (Memory Address Register) and MDR (Memory Date Register). SP can be decremented locally.

The CPU instruction “push r”, where = A or B, has the specification

M [SP] ← r

SP ← SP - 1

How many CPU clock cycles are needed to execute the “push r” instruction?

|

2

|

|

|

3

|

|

|

4

|

|

|

5

|

Question 2 Explanation:

T1: SP → MAR, 2 cycles (as SP is 16 bits and data bus is 8 bits so needs 2 cycles to move data)

T2: 8 → MBR, 1 cycle

T3: M[MAR] ← MBR, 2 cycles (As it is a memory operation)

So, total 5 clock cycles.

T2: 8 → MBR, 1 cycle

T3: M[MAR] ← MBR, 2 cycles (As it is a memory operation)

So, total 5 clock cycles.

Correct Answer: D

Question 2 Explanation:

T1: SP → MAR, 2 cycles (as SP is 16 bits and data bus is 8 bits so needs 2 cycles to move data)

T2: 8 → MBR, 1 cycle

T3: M[MAR] ← MBR, 2 cycles (As it is a memory operation)

So, total 5 clock cycles.

T2: 8 → MBR, 1 cycle

T3: M[MAR] ← MBR, 2 cycles (As it is a memory operation)

So, total 5 clock cycles.