Adder

Question 1 |

Consider the circuit given below which has a four bit binary number b3b2b1b0 as input and a five bit binary number d4d3d2d1d0 as output. The circuit implements:

Binary of Hex conversion

| |

Binary to BCD conversion | |

Binary to grey code conversion | |

Binary to radix-12 conversion |

Question 1 Explanation:

Here ф means 0.

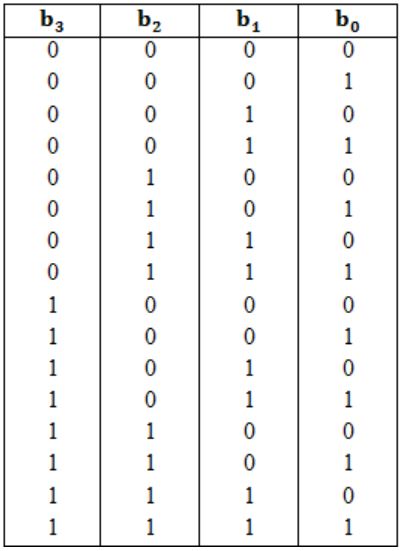

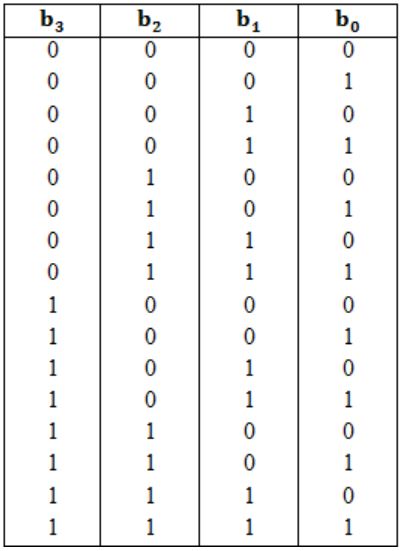

Whenever, b2 = b3 = 1, then only 0100, i.e., 4 is added to the given binary number. Lets write all possibilities for b.

Note that the last 4 combinations leads to b3 and b2 as 1. So, in these combinations only 0010 will be added.

1100 is 12

1101 is 13

1110 is 14

1111 is 15

in binary unsigned number system.

1100 + 0100 = 10000

1101 + 0100 = 10001, and so on.

This is conversion to radix 12.

Whenever, b2 = b3 = 1, then only 0100, i.e., 4 is added to the given binary number. Lets write all possibilities for b.

Note that the last 4 combinations leads to b3 and b2 as 1. So, in these combinations only 0010 will be added.

1100 is 12

1101 is 13

1110 is 14

1111 is 15

in binary unsigned number system.

1100 + 0100 = 10000

1101 + 0100 = 10001, and so on.

This is conversion to radix 12.

Question 2 |

An N-bit carry look ahead adder, where N is a multiple of 4, employs ICs 74181 (4 bit ALU) and 74182 (4 bit carry look ahead generator).

The minimum addition time using the best architecture for this adder is

proportional to N | |

proportional to log N | |

a constant | |

None of the above |

Question 3 |

The number of full and half-adders required to add 16-bit numbers is

8 half-adders, 8 full-adders | |

1 half-adder, 15 full-adders | |

16 half-adders, 0 full-adders | |

4 half-adders, 12 full-adders |

Question 3 Explanation:

For Least Significant Bit we do not need a full adder since initially carry is not present.

But for rest of bits we need full address since carry from previous addition has to be included into the addition operation.

So, in total 1 half adder and 15 full adders are required.

But for rest of bits we need full address since carry from previous addition has to be included into the addition operation.

So, in total 1 half adder and 15 full adders are required.

Question 4 |

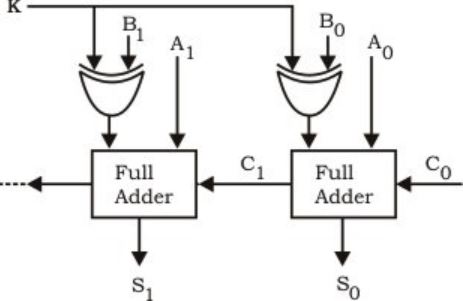

Consider the ALU shown below.

If the operands are in 2's complement representation, which of the following operations can be performed by suitably setting the control lines K and C0 only (+ and - denote addition and subtraction respectively)?

A + B, and A – B, but not A + 1 | |

A + B, and A + 1, but not A – B | |

A + B, but not A – B or A + 1 | |

A + B, and A – B, and A + 1

|

Question 4 Explanation:

The circuits performs

1) A+B when K=0 and C0 = 0. It is binary adder which performs addition of two binary numbers.

2) A - B = A+ B' + 1 when K=1 and C0 = 1 ;

Here XOR gates produce B' if K=1. Since 1⊕b= b'.

"1" in (A+B+1) is coming from C0.

Note: 2's complement of B is (B'+1). 3) A+1 when B=0, K=0, C0= 1.

Increments A.

1) A+B when K=0 and C0 = 0. It is binary adder which performs addition of two binary numbers.

2) A - B = A+ B' + 1 when K=1 and C0 = 1 ;

Here XOR gates produce B' if K=1. Since 1⊕b= b'.

"1" in (A+B+1) is coming from C0.

Note: 2's complement of B is (B'+1). 3) A+1 when B=0, K=0, C0= 1.

Increments A.

There are 4 questions to complete.