Memory-Interfacing

Question 1 |

A 32-bit wide main memory unit with a capacity of 1 GB is built using 256M × 4-bit DRAM chips. The number of rows of memory cells in the DRAM chip is 214. The time taken to perform one refresh operation is 50 nanoseconds. The refresh period is 2 milliseconds. The percentage (rounded to the closest integer) of the time available for performing the memory read/write operations in the main memory unit is _________.

59% | |

60% | |

61% | |

62% |

There are 214 rows, so time taken to refresh all the rows = 214 * 50ns = 0.82 milliseconds

It is given that total refresh period is 2ms. The refresh period contains the time to refresh all the rows and also the time to perform read/write operation.

So % time spent in refresh = (Time taken to refresh all rows / refresh period)*100

= (0.82 ms / 2ms)*100

= 41%

So the % of time for read/write operation = 100 - 41 = 59%

Question 2 |

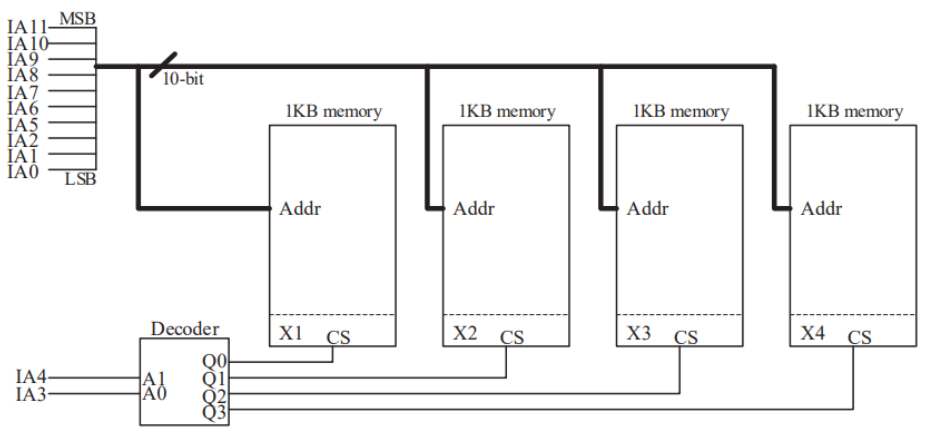

The input memory addresses (IA11–IA0), in decimal, for the starting locations (Addr=0) of each block (indicated as X1, X2, X3, X4 in the figure) are among the options given below. Which one of the following options is CORRECT?

(0, 1, 2, 3) | |

(0, 1024, 2048, 3072) | |

(0, 8, 16, 24) | |

(0, 0, 0, 0) |

Question 3 |

A processor can support a maximum memory of 4GB, where the memory is word-addressable (a word consists of two bytes). The size of the address bus of the processor is at least _________ bits.

32 | |

34 | |

31 | |

33 |

Size of a word = 2 bytes

Therefore, Number of words = 232 / 2 = 231

So, we require 31 bits for the address bus of the processor.

Question 4 |

A main memory unit with a capacity of 4 megabytes is built using 1M 1-bit DRAM chips. Each DRAM chip has 1K rows of cells with 1K cells in each row. The time taken for a single refresh operation is 100 nanoseconds. The time required to perform one refresh operation on all the cells in the memory unit is

100 nanoseconds | |

100*210 nanoseconds | |

100*220 nanoseconds | |

3200*220 nanoseconds |

Required capacity = 4MB

Number of chips needed = 4M*8 bits / 1M x 1-bit = 32 (1M x 1-bit)/(1M x 1-bit) = 32

Irrespective of the number of chips, all chips can be refreshed in parallel.

And all the cells in a row are refreshed in parallel too. So, the total time for refresh will be number of rows times the refresh time of one row.

Here we have 1K rows in a chip and refresh time of single row is 100ns.

So total time required = 1K × 100

= 100 × 210 nanoseconds

Question 5 |

How many 32K × 1 RAM chips are needed to provide a memory capacity of 256K-bytes?

8 | |

32 | |

64 | |

128 |

Needed memory capacity = 256K - bytes = 256K*8 bits

Number of chips needed = 256K*8 / 32K×1 = 64