Memory-Hierarchy

Question 1 |

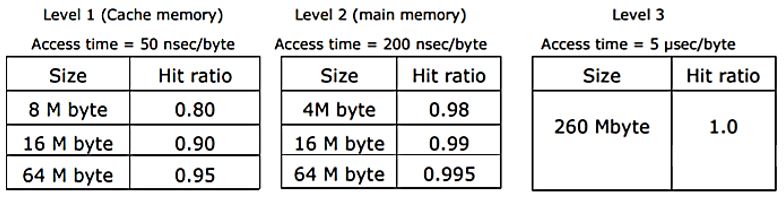

A computer system has a three level memory hierarchy, with access time and hit ratios as shown below:

(a) What should be the minimum sizes of level 1 and 2 memories to achieve an average access time of less than 100 nsec?

(b) What is the average access time achieved using the chosen sizes of level 1 and level 2 memories?

Theory Explanation. |

Question 2 |

Each cache block in WB and WT has a dirty bit. | |

Every write hit in WB leads to a data transfer from cache to main memory. | |

Eviction of a block from WT will not lead to data transfer from cache to main memory | |

A read miss in WB will never lead to eviction of a dirty block from WB. |

Option B: Every write hit in WB need not lead to data transfer from cache to main memory, rather only when that particular block is being evicted there will be transfer from cache to main memory. There can be several write hits in WB before the block is evicted and all those writes will be propagated to the main memory at once. Hence the given statement is false.

Option C: The given statement is true because in WT the writes happen in parallel both in cache and main memory so at the eviction of a block in WT it will not lead to data transfer from cache to main memory.

Option D: A read miss in WB will fetch a new block from main memory and can lead to eviction of a dirty block. Hence the given statement is false.

Question 3 |

A computer system has an L1 cache, an L2 cache, and a main memory unit connected as shown below. The block size in L1 cache is 4 words. The block size in L2 cache is 16 words. The memory access times are 2 nanoseconds. 20 nanoseconds and 200 nanoseconds for L1 cache, L2 cache and main memory unit respectively.

When there is a miss in L1 cache and a hit in L2 cache, a block is transferred from L2 cache to L1 cache. What is the time taken for this transfer?

2 nanoseconds | |

20 nanoseconds | |

22 nanoseconds | |

88 nanoseconds |

And it requires one access of L1 cache and one access of L2 cache. So time taken = 20+2 = 22ns