Digital-Logic-Design

March 18, 2024DSSSB PGT 2018 Female

March 18, 2024Computer-Organization

|

Question 7

|

State True or False with one line explanation

A FSM (Finite State Machine) can be designed to add two integers of any arbitrary length (arbitrary number of digits).

|

True

|

|

|

False

|

Question 7 Explanation:

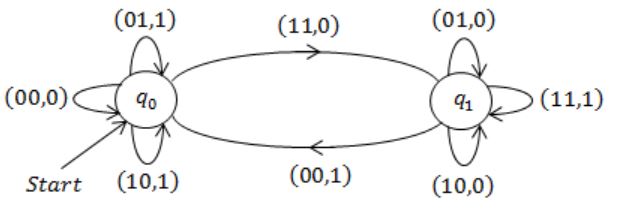

FA or Finite state machine to add two integers can be constructed using two states:

→ q0: Start state to represent carry bit is 0.

→ q1: State to represent carry bit is 1.

The inputs to the FA will be pairs of bits, i.e., 00, 01, 10, 11.

The FA starts in state 1 (since carry is 0) and inputs a pair of bits. If the pair is 11, the FA outputs a ‘0’ and switches to state 2 (since the carry is 1), where the next pair of bits is input and is added to a carry bit of 1.

→ q0: Start state to represent carry bit is 0.

→ q1: State to represent carry bit is 1.

The inputs to the FA will be pairs of bits, i.e., 00, 01, 10, 11.

The FA starts in state 1 (since carry is 0) and inputs a pair of bits. If the pair is 11, the FA outputs a ‘0’ and switches to state 2 (since the carry is 1), where the next pair of bits is input and is added to a carry bit of 1.

Correct Answer: A

Question 7 Explanation:

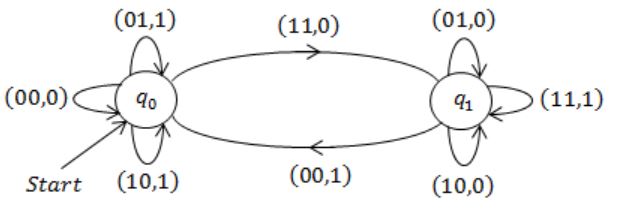

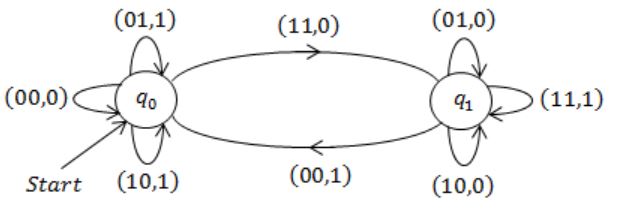

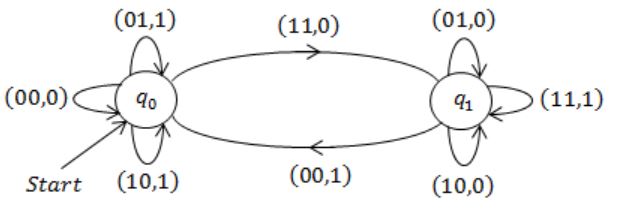

FA or Finite state machine to add two integers can be constructed using two states:

→ q0: Start state to represent carry bit is 0.

→ q1: State to represent carry bit is 1.

The inputs to the FA will be pairs of bits, i.e., 00, 01, 10, 11.

The FA starts in state 1 (since carry is 0) and inputs a pair of bits. If the pair is 11, the FA outputs a ‘0’ and switches to state 2 (since the carry is 1), where the next pair of bits is input and is added to a carry bit of 1.

→ q0: Start state to represent carry bit is 0.

→ q1: State to represent carry bit is 1.

The inputs to the FA will be pairs of bits, i.e., 00, 01, 10, 11.

The FA starts in state 1 (since carry is 0) and inputs a pair of bits. If the pair is 11, the FA outputs a ‘0’ and switches to state 2 (since the carry is 1), where the next pair of bits is input and is added to a carry bit of 1.