NTA UGC NET DEC-2022 Paper-2

Question 1 |

The negation of "Some students like hockey" is:

Some students dislike hockey | |

Every student dislike hockey | |

Every student like hockey | |

All students like hockey |

Question 1 Explanation:

Negation of like is dislike and negation of some one is all(every one)

So negation of some one likes hockey is every student dislikes hockey

So negation of some one likes hockey is every student dislikes hockey

Question 2 |

A relation 'R' is defined on ordered pairs of integers as:

(x,y)R(u,v) if x < u and y > v. Then R is

(x,y)R(u,v) if x < u and y > v. Then R is

Neither a partial order nor an equivalence relation | |

A partial order but not a total order | |

A total order | |

An equivalence relation |

Question 2 Explanation:

A binary relation is an equivalence relation on a nonempty set S if and only if the relation is reflexive(R), symmetric(S) and transitive(T).

A binary relation is a partial order if and only if the relation is reflexive(R), antisymmetric(A) and transitive(T).

From the given relation, it is neither partial order nor equivalence relation.

A binary relation is a partial order if and only if the relation is reflexive(R), antisymmetric(A) and transitive(T).

From the given relation, it is neither partial order nor equivalence relation.

Question 3 |

Suppose you are married and not you and your partner attend a party with three other married couples. Several handshakes took place. No one shook hands with himself (or herself0 or with their partner, and no one shook hands with the same person more than once. After all hand shaking was completed, suppose you asked each person, including your partner, how many hands they had shaken. Each person gave a different answer. How many hands did your spouse shake?

1 | |

2 | |

3 | |

4 |

Question 4 |

Consider the following conditional code, which returns a Boolean values

if ((x>25) && (y>100))

return 'false';

else if((x<=25) && (y<=100)

return 'true';

else if((x>25) && (y<=100)

return 'false';

else

return 'true';

simplify it by filling in the following blank with a single Boolean expression without changing the behaviour of the conditional code.

if( ...........)

return 'true';

else

return 'false';

if ((x>25) && (y>100))

return 'false';

else if((x<=25) && (y<=100)

return 'true';

else if((x>25) && (y<=100)

return 'false';

else

return 'true';

simplify it by filling in the following blank with a single Boolean expression without changing the behaviour of the conditional code.

if( ...........)

return 'true';

else

return 'false';

x>25 | |

x<=25 | |

y>100 | |

y<=100 |

Question 4 Explanation:

According to given conditions, if x value is < = 25 means it will return true and for other values it will return false.

Alone y<=100 won't return true, it should be along with x<=25

Alone y<=100 won't return true, it should be along with x<=25

Question 5 |

Which one of the following types of memory is fastest?

Cache Memory | |

Register Memory | |

Main Memory | |

Secondary Memory |

Question 5 Explanation:

Registers are closest to the processor. Accumulator, Data Register, Programme Counter, General Purpose, and other register types are only a few examples.

Registers are smaller and faster than cache memory. If we count both the memory units on the memory hierarchy, then registers are on the top of the memory hierarchy.

Registers are smaller and faster than cache memory. If we count both the memory units on the memory hierarchy, then registers are on the top of the memory hierarchy.

Question 6 |

The memory size for n address lines and m data lines is given by

2m X n | |

m X n2 | |

2n X m | |

n X m2 |

Question 6 Explanation:

Memory size of n-address lines and m data line is 2^n X m

Question 7 |

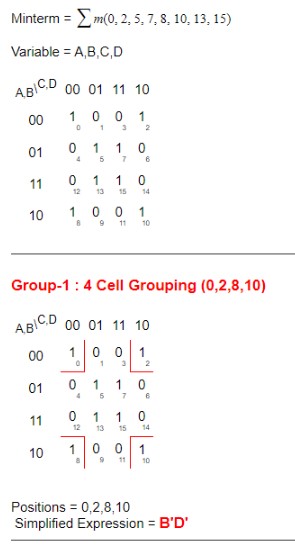

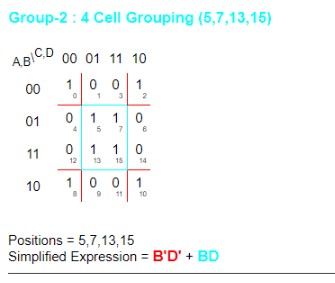

Simplify the following using K-Map

F(A,B,C,D)= Σ(0,2,5,7,8,10,13,15)

F(A,B,C,D)= Σ(0,2,5,7,8,10,13,15)

BD + B'D' | |

AC + A'C' | |

BC + B'C' | |

AD + A'D' |

Question 7 Explanation:

Question 8 |

Consider an unpipelined machine with 10nsec clock cycles which uses four cycles for ALU operations and branches whereas five cycles for memory operation. Assume that the relative frequencies of those operations are: 40% , 20% and 40%, respectively. Due to clock skew and setup pipeline let us consider that the machine adds one nsec overhead to the clock. How much speedup is observed in the instruction execution rate when a pipelined machine is considered.

2 times | |

4 times | |

6 times | |

8 times |

Question 9 |

Machine Level Language is a/an

Assembly Language | |

Low level language | |

High level Language | |

Translating Language |

Question 9 Explanation:

Machine language is another name for low-level language.

The machine language only uses the symbols 1 and 0.

Machine language instructions are all expressed as binary numbers (1s & 0s).

Machine language is immediately understandable by computers.

The machine language only uses the symbols 1 and 0.

Machine language instructions are all expressed as binary numbers (1s & 0s).

Machine language is immediately understandable by computers.

Question 10 |

Which of the following is wrong about the data types?

The number is always positive when qualifier 'unsigned' is used. | |

The number can be positive or negative when the qualifier 'signed' is used. | |

The range of values for signed data types is more than that of unsigned data types | |

The left most bit in unsigned data type is used to represent the value |

Question 10 Explanation:

Except statement-3 all statements are true

Question 11 |

If a constructor 'Date' is declared explicitly and has to be defined outside the class, which of the following is correct?

Date::Date(int dd) {/*...*/} | |

explicit Date::Date(int dd) {/*...*/} | |

Such a constructor cannot be defined | |

Constructor always has to be defined inside the class |

Question 11 Explanation:

Defining a Constructor Outside of the Class :Although the constructor can be defined outside of the class, it must be declared inside class. Use the scope resolution operator while defining a constructor outside of the class.

class class_name {

public:

class_name();

};

// Defining a Constructor Outside of the Class by using :: operator

class_name::class_name()

{

}

class class_name {

public:

class_name();

};

// Defining a Constructor Outside of the Class by using :: operator

class_name::class_name()

{

}

Question 12 |

Which one of the following allows the session to continue?

When a user quits a browser | |

When the user logs out and is invalidated by the servlet | |

When the session is timed out due to inactivity | |

When the user refreshes the browser and there is a persistent cookie |

Question 12 Explanation:

Except the last statement, in all remaining cases the session will be closed.

Question 13 |

Overfitting is expected when we observe that?

With training iterations error on training set as well as test set decreases | |

With training iterations error on training set decreases but test set increases | |

With training iterations error on training set as well as test set increases | |

With training iterations training set as well as test error remains constant |

Question 14 |

Identify the incorrect statement(s).

A candidate key is minimal set of one or more attributes that, taken collectively, allows us to uniquely identify any entity in the entity set. | |

A candidate key for which no proper subset is also a candidate key is called a super key. | |

A super key is a set of one or more attributes that, taken collectively, allows us to uniquely identify any entity in the entity set. | |

A super key for which no proper subset is also a super key is called a candidate key. |

Question 15 |

Consider the two relations below. The primary keys are underlined. Identify all possible foreign key(s) from the options based only on the two relations.

EMP (eid, ename, did)

DEPT (did, dname)

EMP (eid, ename, did)

DEPT (did, dname)

eid | |

did | |

eid, did | |

eid, did, ename |

Question 16 |

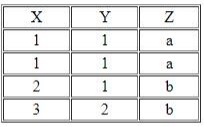

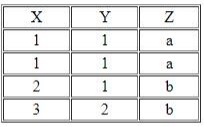

Which of the following statement is correct, according to the following instance of the relational schema R(X,Y,Z)?

X → Y, Z → X | |

Y → Z, Z → X | |

X → Y, X → Z | |

Y → X, X → Z |

Question 17 |

In Linux operating system, when ______ is invoked, it is passed a set of flags that determine how much sharing is to take place between the parent and child tasks.

fork() | |

clone() | |

pthread() | |

thread() |

Question 18 |

The main function of the microkernel is to provide a communication facility between the _____ program and the various ______ that are also running in user space.

Virtual, Processes | |

System, Processes | |

Client, Services | |

Virtual, Services |

Question 19 |

Consider an operating system capable of loading and executing a single sequential user process at a time. The disk head scheduling algorithm used is first come first served (FCFS). If FCFS is replaced by shortest seek time first (SSTF) and the vendor claims 50% better benchmark results. What is the expected improvement in the I/O performance of user programs?

50% | |

100% | |

25% | |

0% |

Question 20 |

For the following set of processes scheduled using FCFS policy, determine the average waiting time. Assume that the processes arrived in the order P1, P2, P3, P4.

8 | |

16 | |

32 | |

48 |

Question 21 |

Which of the following is not a Non functional requirement?

Portability | |

Security | |

Scalability | |

User interaction |

Question 22 |

COCOMO Stands for____

Consumed cost model | |

Constructive cost model | |

Common control model | |

Composition cost model |

Question 23 |

Modifying the software to match changes in the ever changing environment is called as

Adaptive maintenance | |

Corrective maintenance | |

Perfective maintenance | |

Preventive maintenance |

Question 24 |

For a function of two variables, boundary value analysis yields,

4n+3 test cases | |

4n+1 test cases | |

n+4 test cases | |

2n+4 test cases |

Question 25 |

How many different trees are possible with 'n' nodes?

n-1 | |

2n -1 | |

2n | |

2n -n |

There are 25 questions to complete.